NanoSOI Fabrication Service

Fabrication of photonic integrated circuits with rapid turnaround times, high resolution, and proven optical performance

Rapid fabrication service for prototyping silicon photonic integrated circuits

The NanoSOI Fabrication Service is a foundry service for the fabrication of photonic integrated circuits. Superior line-edge roughness, high throughput, and negligible stitching errors are guaranteed with the use of a state-of-the-art 100 keV electron-beam lithography system. Our anisotropic plasma etch process provides smooth sidewalls and low propagation loss. Optional standard process steps include oxide cladding deposition, metallization and deep trench etching to create passive and thermo-optic photonic devices with grating couplers or edge couplers. We also offer custom options including partial etch depths, oxide windows, and thermal isolation trenches.

There are two options for accessing the NanoSOI Fabrication Service. Multi-project wafer (MPW) runs are scheduled once every six to eight weeks. Standard processes and immediate pricing are available for these runs. Dedicated runs are for projects requiring custom options. Timelines for these runs are flexible, and quotations are customized for each run.

Easy-to-use online system

Visit the NanoSOI Design Center for pricing, online design submission, design verification, process design kits, and many more resources

Designs are submitted online using the NanoSOI Design Center. Design files are provided to us in Calma Graphics Data System II (GDSII) format, with database units of 1 nanometre. The latest design rules, layout tutorials, the process design kit, and an online design verification tool are all located at the NanoSOI Design Center.

Process Design Kits (PDKs) are available for KLayout, and the Luceda Photonics Design Platform.

The run schedule and pricing for multi-project wafer runs is also available online through the Design Center. The fabrication run schedule can be found here.

High performance integrated photonic circuits with low propagation loss

Examples of devices fabricated with our process include subwavelength grating couplers and photonic crystal cavities

We track our optical propagation loss using test structures on every multi-project wafer run. The test structures are comprised of 500 nm-wide silicon strip waveguides with 2.2 μm thick cladding oxide. Cut-back loss measurements are performed by varying the length of the waveguide, measuring the total insertion loss of each device, and performing a linear fit of loss versus waveguide length. The average propagation loss for fully-etched 220 nm SOI devices is shown here:

|

Polarization |

Straight Waveguide Loss |

Curved Waveguide Loss |

|---|---|---|

| TE | 1.2 dB/cm | 3.0 dB/cm |

| TM | 1.7 dB/cm | 2.3 dB/cm |

Detailed measurement data, including spectral scans, can be provided by request.

Available Process Options

Several of these processes are available in multi-project wafer (MPW) runs and dedicated runs; some are available only in dedicated runs.

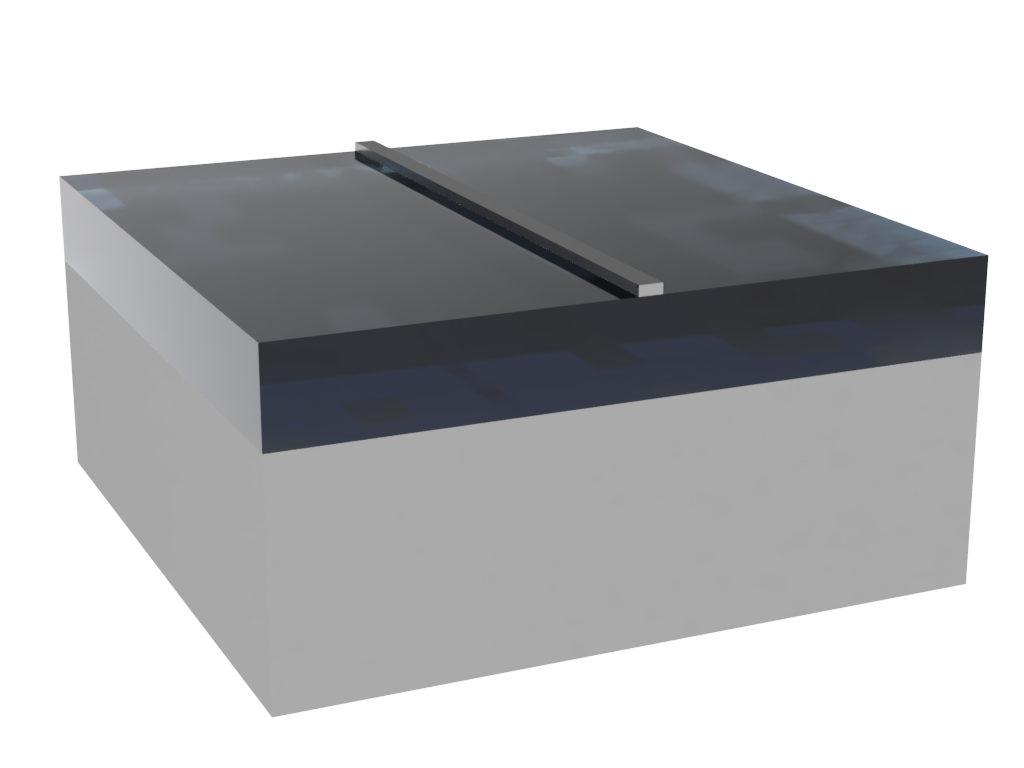

Silicon Device Layer

Feature sizes as small as 60 nm with high performance electron beam lithography. Available in MPW and dedicated runs.

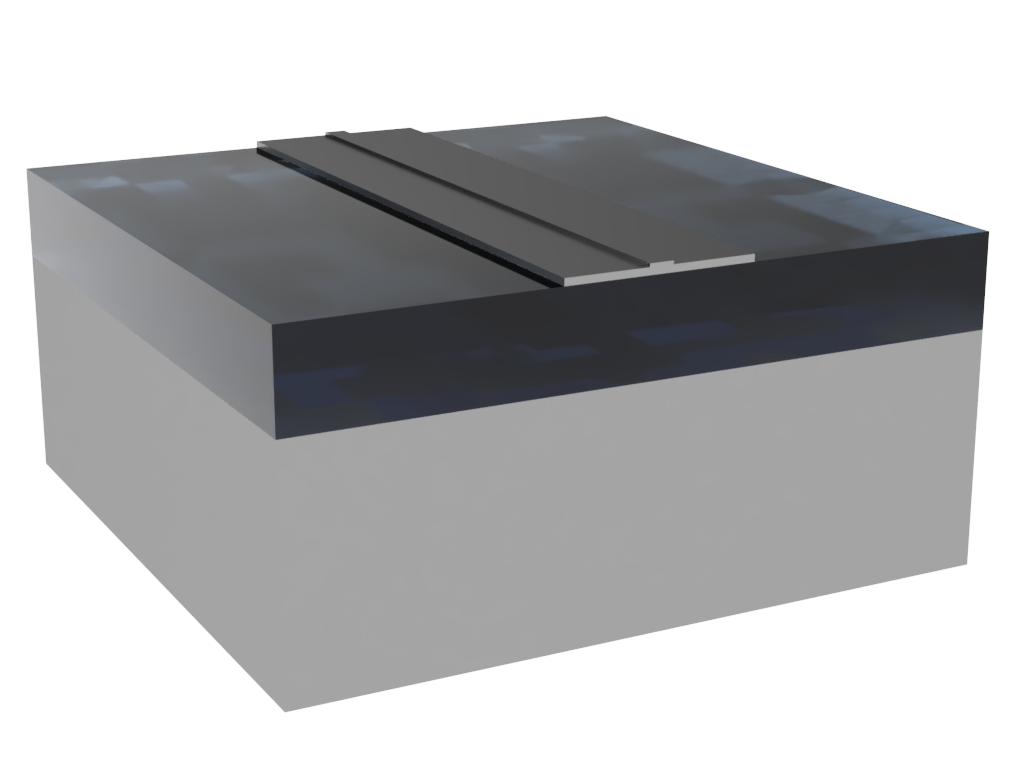

Our silicon patterning process involves the definition of nano-scale features in silicon-on-insulator (SOI) using electron beam lithography (EBL) and reactive ion etching (RIE) processes. The substrate is a 220 nm silicon device layer with a 2 µm buried oxide layer and 725 µm handle wafer.

The patterning process begins by cleaning and spin-coating a material that is sensitive to electron beam exposure. A device pattern is defined into this material using 100 keV EBL. Once the material has been chemically developed, an anisotropic ICP-RIE etching process is performed on the substrate to transfer the pattern into the underlying silicon layer. The etch is performed until there is no remaining silicon and the underlying oxide layer is exposed.

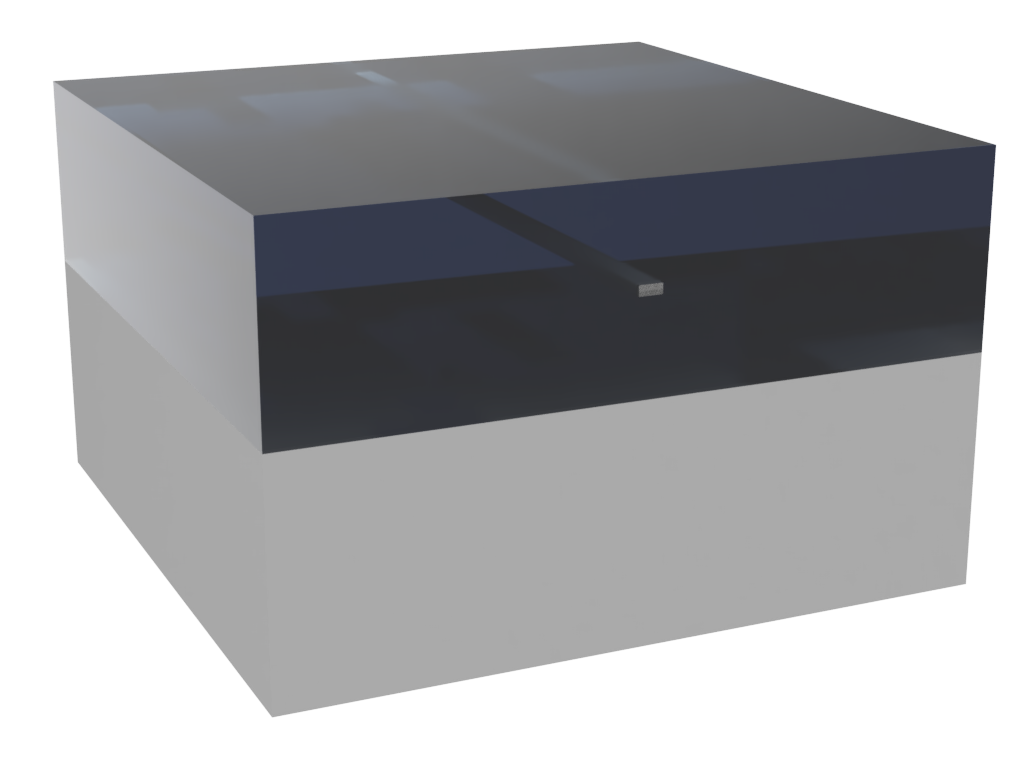

Oxide Deposition

Cladding oxide to improve device performance. Available in MPW and dedicated runs.

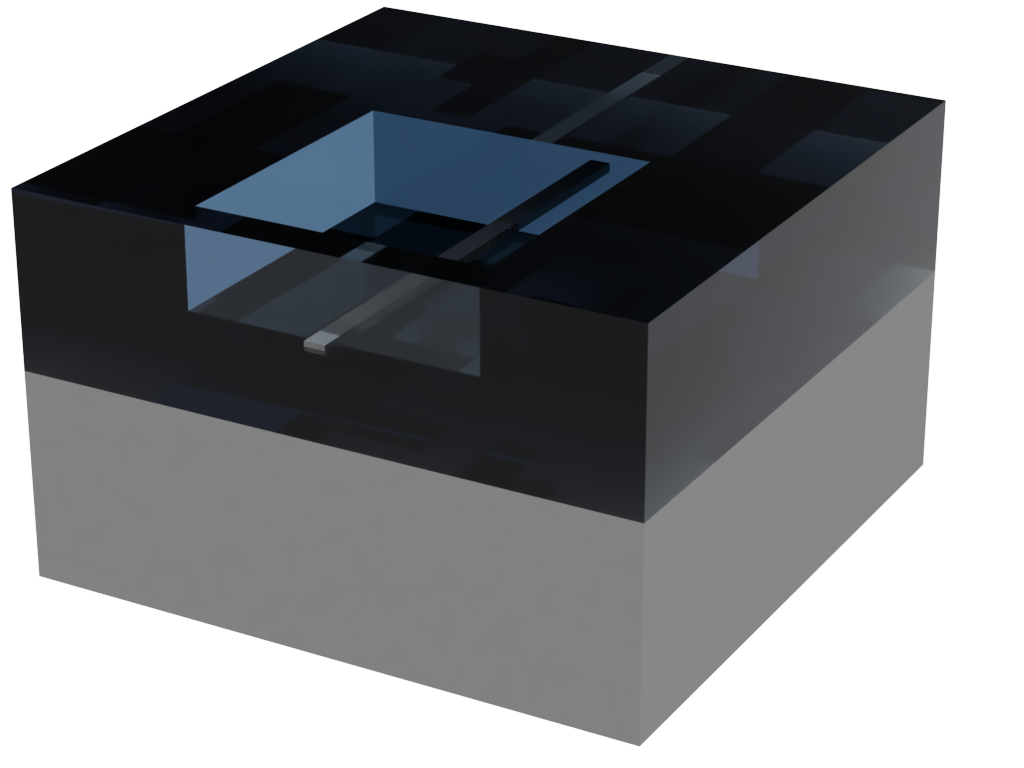

If the photonic devices require isolation from the outside environment, silicon dioxide cladding is deposited using chemical vapour deposition (CVD). Our standard oxide cladding thickness is 2.2 µm. The oxide deposition process can be combined with the tri-layer metallization process to fabricate active photonic devices with thermal tuning.

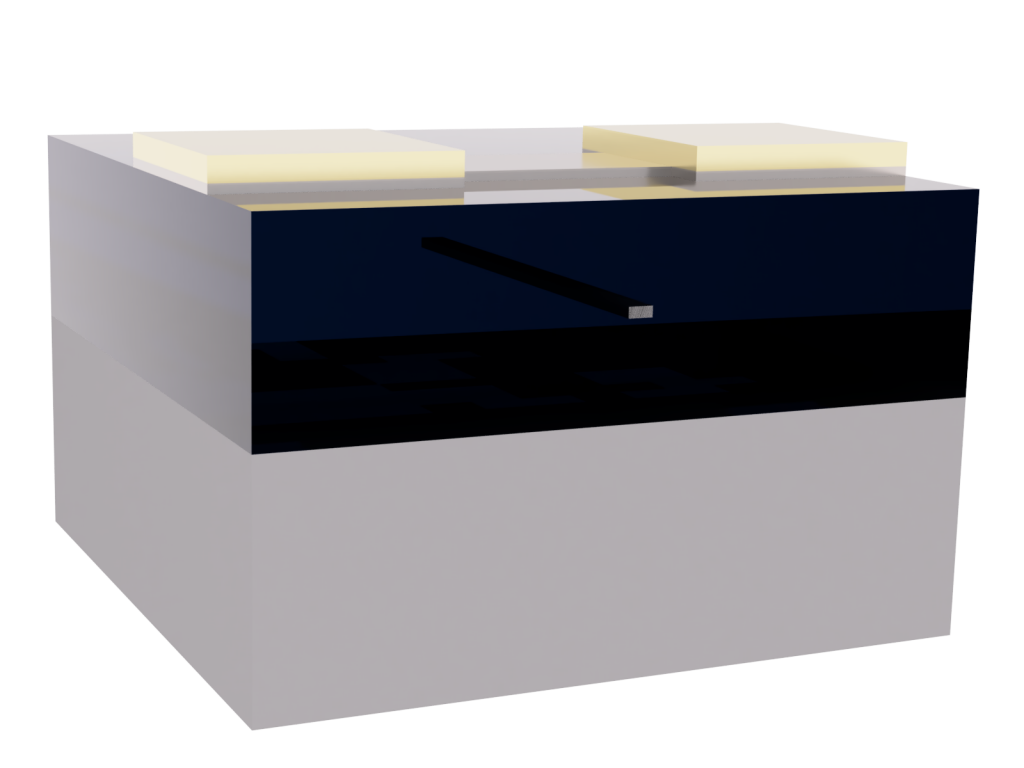

Tri-Layer Metallization

Heaters for thermal tuning of photonic devices. Available in MPW and dedicated runs.

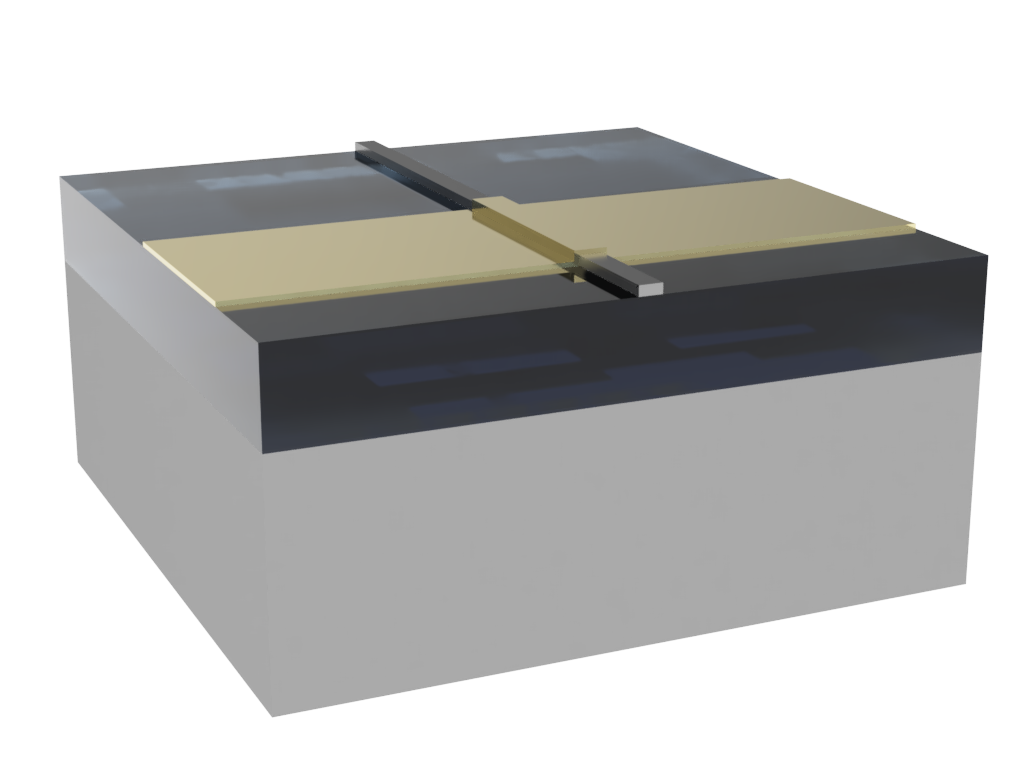

Tri-layer metallization creates compact heater devices using a high-resistance titanium-tungsten alloy (TiW). Contact with the heaters is made with a low-resistance titanium-tungsten/gold bi-layer (TiW/Au). The use of two metals increases the electrical efficiency of the devices, as the majority of the heat generation can be targeted to a specific area of the chip. Using a bi-layer for the routing layer ensures good electrical contact between the routing layer and the heater layer, reduces the contact resistance, and improves uniformity.

A third layer consisting of silicon dioxide is used as passivation to protect the heaters from oxidation damage. The oxide is etched away to create windows over the gold pads to expose them for probing or wire bonding.

|

Metal |

Thickness |

Bulk Resistivity |

Sheet Resistance |

|---|---|---|---|

| TiW Heater Layer |

200 nm | 0.61 μΩ-m | 3.03 Ω/sq |

| TiW/Au Routing Bi-layer | 200 nm TiW + 400 nm Au | 0.06 μΩ-m | 0.14 Ω/sq |

| Silicon Dioxide Passivation Layer | 300 nm | N/A | N/A |

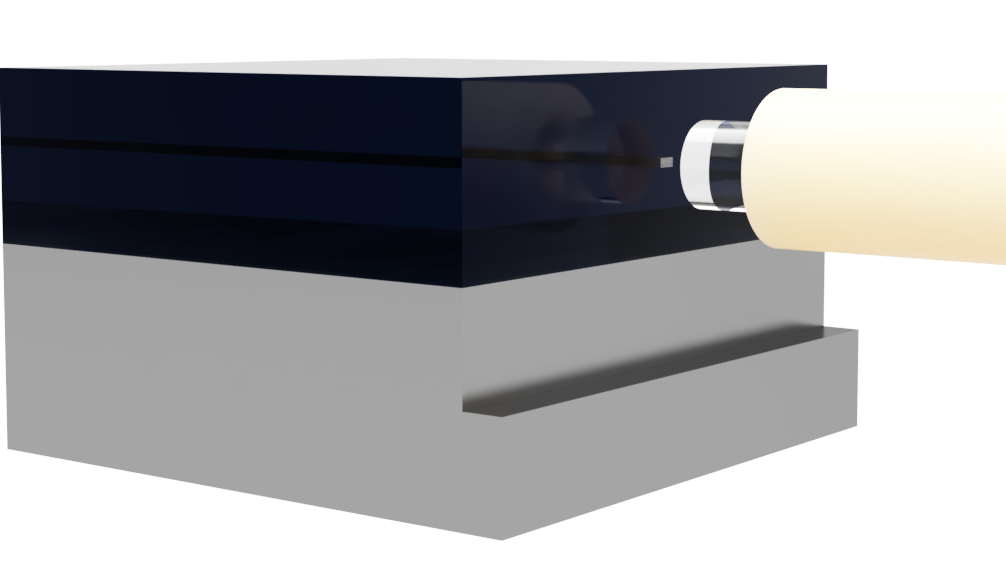

Deep Trench Process

Edge couplers for efficient input and output of light. Available in MPW and dedicated runs.

We use a deep-etch process to create smooth trenches around the perimeter of the chip. This allows for efficient edge-coupling of light into nano-tapered waveguides and sub-wavelength gratings.

The trench is patterned around an 8.78 x 8.78 mm area centered on the submitted GDSII design. The deep-etch process is used to remove the cladding, buried oxide, and 250 microns of the silicon substrate, while creating smooth facets in the silicon device layer. The remaining silicon substrate is diced with a saw. The final result is die with clearance on all four sides for fiber edge-coupling.

The deep trench process can also be used for fabrication of thermal isolation trenches. Trenches as deep as 100 µm can be etched all the way into the handle silicon. This process enables fabrication of thermal isolation trenches in photonic integrated circuits which effectively minimizes thermal crosstalk.

Partial silicon etching

Customized silicon etch depths for rib waveguides. Available in dedicated runs only.

Partial silicon etching is available only in dedicated runs. Partial etching can be used to create rib waveguides or grating couplers. We can customize the etch depth for your specific application. By using high accuracy electron beam lithography alignment, we can align the partially etched layer to the fully etched layer with an error of less than 50 nm. This allows for low-loss transitions between strip and rib waveguides.

Oxide Window Open

Windows in the cladding oxide to expose silicon features. Available in dedicated runs only.

Selective etching of the cladding oxide over silicon features is performed to create windows in the oxide where the silicon devices are exposed to ambient conditions. One potential application is in integrated photonic sensors. With windows in the oxide opened over the silicon devices, the devices can interact with ambient conditions and perform sensing operations. This process is available only on dedicated runs.

Other Dedicated Run Options

These options are available in dedicated runs only.

In addition to the popular process options listed here, we have many other custom options available for dedicated runs. Some examples include:

- Direct metal on silicon (shown here)

- Positive-tone processing for photonic crystals

- 300 nm or 500 nm silicon device layer thickness

For the full list of our available processes, please click the button below to view our dedicated run information at the NanoSOI Design Center.