Process Overview

Silicon Device Layer

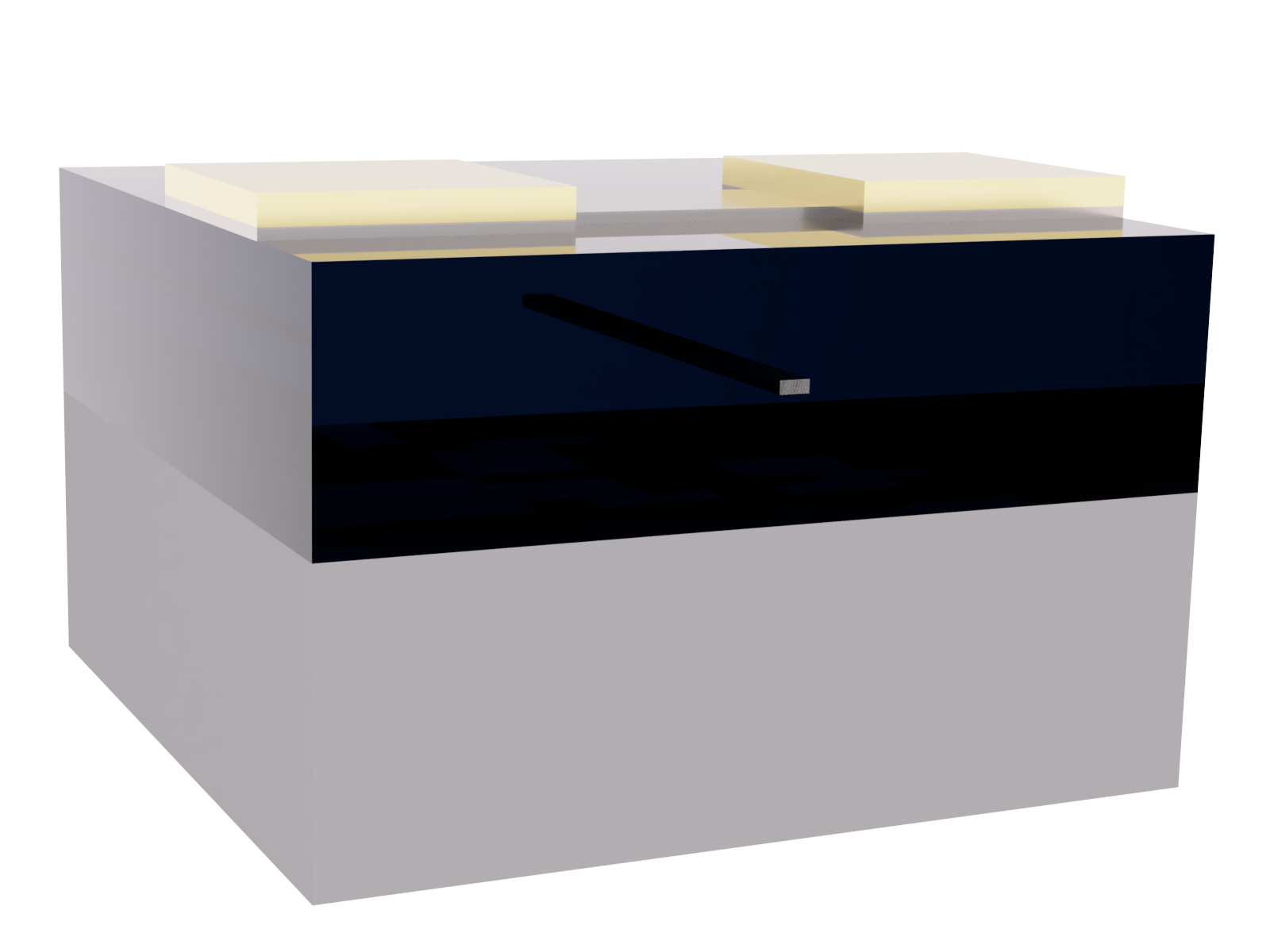

The foundation of the NanoSOI fabrication process is the device layer. Photonic waveguides capable of light propagation are patterned using 100 keV electron beam lithography technology. In our multi-project wafer runs, fully-etched devices (etched down to the buffer oxide, as shown in the above diagram) are created using an e-beam mask material and anisotropic ICP-RIE etching process. The minimum feature size is 60 nm and the minimum feature spacing is 70 nm, where duty cycle of surrounding region is ≤ 50%. For duty cycles greater than 50%, resolution will decrease further because of proximity effects.

Custom etch depth and multiple etch depths of the device layer are available through dedicated runs. Please contact support@appliednt.com to inquire.

Substrate:

We currently offer one substrate in our multi-project wafer (MPW) runs:

| Device Layer Type | Device Layer Thickness | Buffer Oxide Layer Thickness | Silicon Handle (Substrate) Thickness | Wafer Manufacturer |

|---|---|---|---|---|

| Silicon | 220 nm | 2.0 μm | 725 μm | SOITEC S.A. |

Other substrates with varying silicon layer thickness are available through dedicated runs. Please contact support@appliednt.com if you require a different substrate.

Propagation Loss Measurements:

Applied Nanotools periodically measures the optical propagation loss using test structures. The test structure is a straight 500 nm-wide silicon strip waveguide with a 2.2 μm thick cladding oxide. Cut-back loss measurements are performed by varying the length of the waveguide from 0 to 3 centimetres, measuring the total insertion loss of each device and performing a linear fit on loss vs. waveguide length. Both straight and curved waveguide segments are used. The average propagation loss for fully-etched 220 nm SOI devices is tabulated below:

| Polarization | Straight Waveguide Loss | Curved Waveguide Loss |

|---|---|---|

| TE | 1.2 dB/cm | 3.0 dB/cm |

| TM | 1.7 dB/cm | 2.3 dB/cm |

These results are averaged over two sets of test arrays. Each set was separated by 9 mm. Detailed measurement data, including spectral scans, can be provided by request.

Proximity Effects:

A limitation of electron beam lithography technology is electron scattering effects when exposing patterns into the mask. During the file preparation process, we apply a proximity effect correction algorithm to the design to mitigate these effects. However, extreme cases such as large areas/pads (> 10 × 10 μm) in close proximity to high-resolution features or small feature spacings are difficult to correct for. Please inquire with us if your design has large areas to be exposed in conjunction with high resolution features or small spacings. For regions with duty cycle (pattered area ÷ total area) larger than 50%, the minimum dimension and minimum spacing will be larger than what is specified in the design rules. The examples below show acceptable designs (green check mark) and designs with minimum features greater than 60 nm (red X).

Sidewall Angle:

Imperfections in the mask and etching process will create an angle to the sidewall of the waveguide. The sidewall angle of silicon waveguides fabricated with our process is approximately 88 degrees (improved from 82 degrees, prior to the January 2021 MPW run). We aim to have the waveguide dimensions match the GDS design with proximity and etch bias corrections applied during layout processing.

Oxide Cladding

A cladding oxide layer can be deposited onto the device if required. The deposition is performed using a plasma-enhanced chemical vapour deposition (PECVD) process. The standard oxide deposition thickness for MPW runs is 2.2 µm, which is sufficient for most thermal and optical isolation applications. The oxide deposition process can be combined with our tri-layer heater metallization process to fabricate thermo-optic photonic devices that can be controlled with temperature.

Custom oxide thicknesses up to 3 µm can be requested but are subject to an additional surcharge. Please contact support@appliednt.com to inquire.

Direct Metallization

This option is available in dedicated runs only. The purpose of direct metallization is to create bonding and/or probing pads and to pattern coarse electronic pathways directly on the silicon devices. This metallization process uses photolithography to define the metal areas (minimum 10 µm feature size) to within a 2 µm alignment precision to the underlying silicon layer. Metals are deposited on the substrate using electron-beam evaporation and thickness can be controlled to an accuracy of ± 5% of the overall thickness. Oxide cladding cannot be deposited on the device before direct metallization is performed. For MPW runs, the metal properties are as follows:

| Metal | Thickness |

|---|---|

| Gold (with 4 nm Cr adhesion layer) |

100 nm |

Custom metals such as Al or Cr are available through dedicated runs. Please contact support@appliednt.com to inquire.

Tri-Layer Metallization

*Protective oxide layer not shown

The purpose of tri-layer metallization is to create compact heater devices using a high-resistance metal and interface with the heater devices using a low-resistance routing layer. The use of two metals increases the electrical efficiency of the devices, as the majority of the heat generation can be targeted to a specific area of the chip with the high resistance metal. The oxide passivation layer protects the heaters from damage due to oxidation. The two metal layers and oxide passivation layer are patterned using photolithography.

The heater layer (Layer 11) uses a titanium-tungsten alloy to implement the high-resistance heater devices. The TiW alloy we use is 90% W, 10% Ti by weight. This information can be used to estimate the film density and specific heat capacity. We can also calculate the electrical conductivity from the bulk resistivity shown in the table below as 1/(0.61 x 10-6) = 1.64 x 106 S/m. The thermal conductivity of TiW can be estimated from the electrical conductivity using the Weidemann-Franz law for a specific temperature. For room temperature (298 K), thermal conductivity is (2.44 x 10-8 W-Ohm-K-2)(1.64 x 106 1/Ohm-m)(298 K) = 11.9 W/m-K. During high temperature operation, the thermal conductivity will change. For example, at 100 degrees C, it becomes (2.44 x 10-8 W-Ohm-K-2)(1.64 x 106 1/Ohm-m)(373 K) = 14.9 W/m-K.

The routing layer (Layer 12), which can consist of wider electrical traces or bonding/probing pads, is made out of a titanium-tungsten/gold bilayer. Using a bilayer for the routing layer ensures good electrical contact between the routing layer and the heater layer with low contact resistance. The bilayer also ensures that the routing layer is uniform layer with no height changes. A blanket layer of oxide is then deposited on the chips and the probing pads are exposed using the bond pad open layer (Layer 13). The alignment tolerance between the Si and TiW layers, and between the TiW and TiW/Au layers, is less than 1 μm.

Below are the specifications for the three layers:

| Metal | Thickness | Bulk Resistivity | Sheet Resistance | Maximum Current Density |

|---|---|---|---|---|

| Ti/W Alloy Heater Layer |

200 nm | 0.61 μΩ-m | 3.03 Ω/sq. | 70 mA/μm2 |

| TiW/Au Bilayer Routing Layer |

200 nm TiW + 400 nm Au | 0.06 μΩ-m | 0.14 Ω/sq. | N/A |

| Silicon Dioxide Passivation Layer |

300 nm | N/A | N/A | N/A |

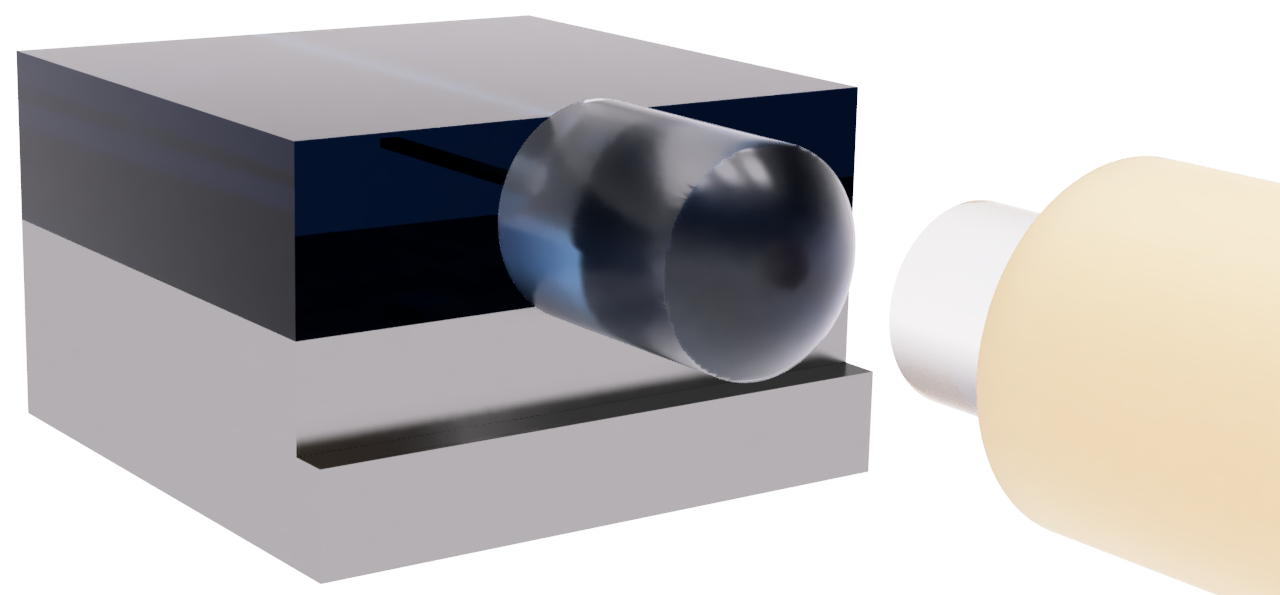

Edge Couplers

With our deep-etch process, trenches 250 microns deep are etched along the perimeter of the chip to allow for edge-coupling with optical fibers. Devices such as nano-tapered waveguides and sub-wavelength gratings increase edge-coupling efficiency. The trench is patterned around an 8.78 x 8.78 mm enclosed area, centered on the submitted GDSII design. A deep-etch process is then used to etch through the cladding, silicon device layer, buried oxide, and through 250 microns the underlying silicon substrate. The remaining silicon handle wafer is diced with a saw to separate the chips. The etch and dice process occurs on all four sides of the chip.

We advise extending the silicon features at least 10 µm across the deep-etch boundary to eliminate any potential alignment errors. For more details about design of a deep trench layout, please see our deep trench design example.

Facet-attached Micro Lens

A facet-attached micro lens (FaML) can be attached to an edge coupler using a two-photon lithography process to achieve low-loss coupling (<3 dB) to mode-matched microlens-attached fiber(s). The field emitted from the edge coupler is expanded from 3 μm to 25 μm to allow relaxed alignment for fast and easy coupling. The fabrication process is performed by Dream Photonics Inc. after the photonic integrated circuit chips have been fabricated by ANT. The edge coupler used for this process is designed by Dream Photonics Inc. and the deep trench etching process is required for the edge couplers. Additional qualities include low polarization-dependent loss (0.5 dB) and large bandwidth operation (>100 nm). The polymer of the microlenses is also rated for high power handling (>700 mW at telecom wavelengths), Telcordia Ref. 3.3.2.2: 225 cycles of -40°C to +85°C (>200 h), and Telcordia Ref. 3.3.2.3: 85°C/85% humidity, 3500 h.

For more details, please see the FaML example.